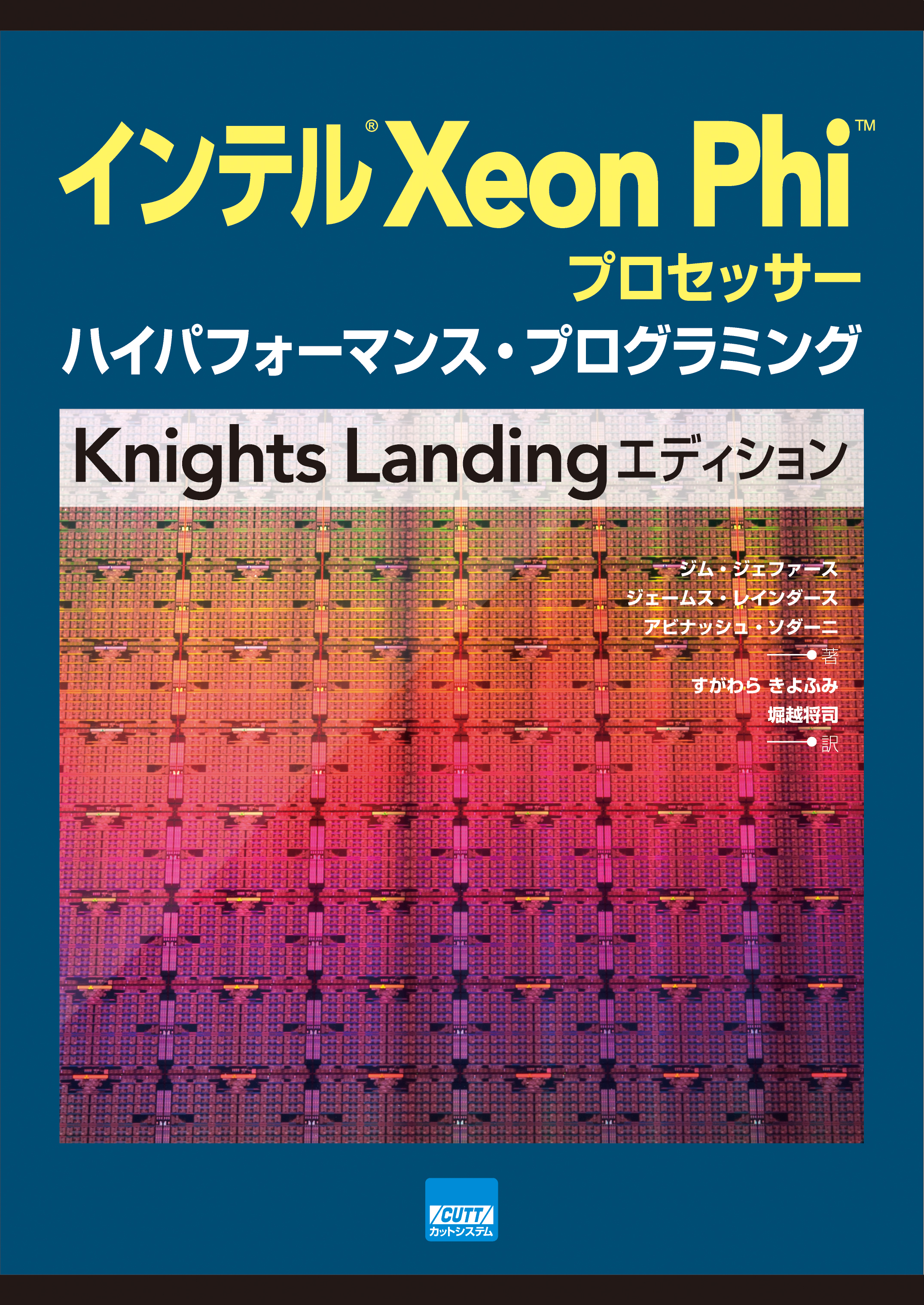

本書は、前作『インテル® Xeon Phi™ コプロセッサー・ハイパフォーマンス・プログラミング』(邦訳版2014年刊行)の内容を置き換えて、最新のインテル® Xeon Phi™ プロセッサー(開発コード「Knights Landing」)に含まれる多くの拡張機能を最大限に活用する並列プログラミング手法に焦点を当てています。 本書は、読者がメニーコア・プログラミングの知識をある程度持っていると仮定して書かれています。

第I部「Knights Landing」では、Knights Landing に注目し、アーキテクチャー、高帯域幅メモリー、クラスターモード、および統合ファブリックについて説明します。他のコンピューターでもそうであるように、アプリケーションをチューニングする可能性を見出すには、それらを理解する必要があります。この部ではこの理解度を深めます。

第II部「並列プログラミング」では、メニーコアへスケールするためアプリケーション・プログラミングで考慮すべき内容に注目します。第7章は、並列処理を実装するためにコードを変更することは、革新に対する進化であることを説明します。

第III部「秘訣」では、実際の並列アプリケーションに注目し、Knights Landing での特定の結果と最適化の注意事項と例をまとめています。ここで見つけられる多くのテクニックは、Knights Landing を含む多くのマルチコアおよびメニーコア・プロセッサーのパワーを活用する方法をもたらすでしょう。

【目次】

- 第 Ⅰ 部 Knights Landing

第 1 章 はじめに

第 2 章 Knights Landing の概要

第 3 章 MCDRAM のプログラミングとクラスターモード

第 4 章 Knights Landing アーキテクチャー

第 5 章 インテル Omni-Path ファブリック

第 6 章 マイクロアーキテクチャーの最適化アドバイス

- 第 Ⅱ 部 並列プログラミング

第 7 章 Knights Landing 向けプログラミングの概要

第 8 章 タスクとスレッド

第 9 章 ベクトル化

第 10 章 ベクトル化 Advisor

第 11 章 インテル SDLT によるベクトル化

第 12 章 インテル AVX-512 組込み関数によるベクトル化

第 13 章 パフォーマンス・ライブラリー

第 14 章 プロファイルとタイミング

第 15 章 MPI

第 16 章 PGAS プログラミング・モデル

第 17 章 ソフトウェア定義の可視化(SDV)

第 18 章 Knights Landing へのオフロード

第 19 章 電力解析

- 第 Ⅲ 部 秘訣 (Pearls)

第 20 章 LAMMPS における古典的な分子動力学の最適化

第 21 章 ハイパフォーマンス地震シミュレーション

第 22 章 気象研究と予測 (WRF)

第 23 章 N 体シミュレーション

第 24 章 マシンラーニング

第 25 章 Trinity ワークロード

第 26 章 量子力学

書籍の宅配をご希望される方は「カットシステム直販案内」をご利用ください。

C/C++、Fortran プログラマーのための

インテル® Parallel Studio XE 2015 入門

Windows、Linux および Mac OS X 向け アプリケーション開発の統合開発スイート

本書では、インテル® Parallel Studio XE 2015 製品の使い方を解説しています。多くの章は前バージョンである、インテル® Parallel Studio XE 2013 にも適用できます。

近年のプログラミング環境は複雑になり、単純にコンパイラーだけでプロジェクトが作成されることはほとんどありません。プロジェクトの設計、コーディング、ビルド、最適化、デバッグ、パッケージ化などの一連の手順が 1つの IDE として提供される傾向にあります。特に本書が対象とする Windows および Linux 上では、IDE は多くの開発者に利用されています。インテル® Parallel Studio XE 2015 は単独の IDE ではなく、すでに開発者が利用している Visual Studio や Eclipse、Xcode 環境へのプラグイン機能として、最新のプロセッサーやプラットフォームのパフォーマンスを最大限に活用できるよう設計されたコンパイラー、ライブラリー、最適化ツール、デバッグツール、設計支援ツールなどを提供します。

【目次】

- 第 1 章 インテル® ソフトウェア開発製品とは

- 第 2 章 インテル® Parallel Studio XE 2015 製品概要と入手方法

- 第 3 章 インテル® Parallel Studio XE のインストールとアンインストール(Windows 編)

- 第 4 章 インテル® Parallel Studio XE のインストールとアンインストール(Linux 編)

- 第 5 章 インテル® Parallel Studio XE のインストール(OS X 編)

- 第 6 章 インテル® Parallel Studio XE 2015 の使い方

- 第 7 章 インテル® Parallel Studio XE 2015 の各コンポーネントの詳細

- 第 8 章 インテル® Parallel Studio XE 2015 を使用したパフォーマンス・チューニング・サイクル

- 第 9 章 パフォーマンス・チューニング・サイクル詳細(パフォーマンスの計測と最適化)

- 第 10 章 SIMD 命令を使用してベクトル化を有効にするには

- 第 11 章 キャッシュを有効に利用するには

書籍の宅配をご希望される方は「カットシステム直販案内」をご利用ください。

Microsoft Kinect の登場以来、マウスやキーボードに代わる新しい PC の操作方法として、センサーデバイスによる「NUI(ナチュラル・ユーザー・インタフェース)」が注目されています。ジェスチャーや音声コマンドなど、人間の五感や自然な行動による直感的な操作を可能とするため、PC を使い慣れていない若年層や高齢者にも好評です。

本書がテーマとしている「インテル® RealSense™(リアルセンス)テクノロジー」は、CPU のトップメーカーである Intel 社が開発したセンサー入力技術です。専用の 3D カメラでユーザーを捉えることで、NUI を実現します。対応アプリの開発は、無償公開されている「インテル® RealSense™ SDK」を用いて C# や C++ などで行います。昨今、ユーザーが爆発的に増えている「Unity」にも対応しており、ゲーム開発者からも注目されています。本書では、「Intel® RealSense™ SDK」の基本 API はもとより、応用としてのアプリ開発例や Tips を紹介します。Visual Studio、Unity 5、openFramework など人気の開発環境を使った手順も解説。

» 目次詳細はこちらインテル® Xeon Phi™ コプロセッサーは、これまでの IA プロセッサーとは異なるアプローチが必要であり、製品化に至るまでソフトウェア開発についてもいろいろ試行錯誤が行われました。プロトタイプは作られましたが、製品化には至らなかったものもあります。最終的に決まったことは、「新しい言語やプログラミング・モデルを習得することなく、容易に新しいハードウェアを利用できるようにする」ということでした。そのため、すでに並列プログラミングやベクトル化の経験がある開発者の方が本書をご覧になると、コプロセッサーを利用するために追加された機能をいち早くご理解いただけると思います。

本書はすぐにプログラミングを始められるように構成されています。簡単な紹介に続いて、プログラミングに関する説明を行い、パフォーマンスを達成する方法を示すプログラミング例を通して皆さんの意欲を高めます。本書の第 1 章から第 5 章では、関連するテクノロジーや製品の関係を整理、構築し、第 6 章から第 14 章はどの順番でもお読みいただけるように各章で完結しています。第 6 章以降は、プログラミング例を用いてシステムの個々の要素を詳しく説明し、読者が求める情報を探しやすいように構成しています。

【目次】

- 第 1 章 概要

- 第 2 章 高性能なサーキットでの運転

- 第 3 章 のどかな田舎道でのレース

- 第 4 章 市街地の運転:現実的なコードサンプルの最適化

- 第 5 章 多くのデータ(ベクトル)

- 第 6 章 多くのタスク(スレッドではない)

- 第 7 章 オフロード

- 第 8 章 コプロセッサー・アーキテクチャー

- 第 9 章 コプロセッサーのシステム・ソフトウェア

- 第 10 章 コプロセッサー上のLinux

- 第 11 章 算術ライブラリー

- 第 12 章 MPI

- 第 13 章 プロファイルとタイミング

- 第 14 章 まとめ

書籍の宅配をご希望される方は「カットシステム直販案内」をご利用ください。

本書は、並列プログラミングにおけるデザインパターンを示す手引書です。パターンの概念を文書や図表だけで理解いただくのは容易でないため、本書では随所にサンプルコードが紹介されています。すでに業界標準となっている OpenMP* やインテル® TBB、インテル® Cilk™ Plus などによるパターンの実装例が示されています。C/C++、そして一部 Fortran を利用する開発者の方々に役立つ書籍です。

【目次】

- 第 1 章 概要

- 第 2 章 背景

- 第 3 章 パターン

- 第 4 章 マップ

- 第 5 章 集合

- 第 6 章 データ再構成

- 第 7 章 ステンシルと繰り返し

- 第 8 章 フォーク・ジョイン

- 第 9 章 パイプライン

- 第 10 章 フォワード地震シミュレーション

- 第 11 章 K-平均法クラスタリング

- 第 12 章 bzip2データ圧縮

- 第 13 章 マージソート

- 第 14 章 サンプルソート

- 第 15 章 コレスキー分解

- 付録A 参考資料

- 付録B Cilk Plus

- 付録C TBB

- 付録D C++11

- 付録E 用語集

書籍の宅配をご希望される方は「カットシステム直販案内」をご利用ください。

インテル® Cilk™ Plus は、C/C++ プログラマーのための、インテル® コンパイラーに実装される並列プログラミング手法で、並列プログラミングを導入する最も簡単な方法です。本書は、インテル® Cilk™ Plus の入門書として書かれていますので、是非、この機会に並列プログラミングをお試しください。

【目次】

- 第 1 章 インテル Cilk Plus とは

- 第 2 章 Cilkプログラミングで知らなければいけないこと

- 第 3 章 レデューサー

- 第 4 章 Cilkプログラムの実行モデル

- 第 5 章 競合とロック

- 第 6 章 Cilkプログラミングを始める

- 第 7 章 Cilkプログラムのデバッグと最適化

- 第 8 章 Cilk Plusのその他の機能

- 第 9 章 Cilkのサンプルコード

- 第 10 章 Cilkのバージョン間の相違

- 付録 A Cilkの関連する情報

- 付録 B Cilkのレデューサーに関する情報

- 付録 C サンプルコードに関する情報

- 付録 D 用語集

書籍の宅配をご希望される方は「カットシステム直販案内」をご利用ください。

C/C++ コンパイラーの利用経験と知識があり、既存のシングルスレッドプログラムのマルチスレッド化を検討されているユーザー向けに、gcc、Visual C++、インテルC++ コンパイラーがサポートするOpenMP の機能を使用し、容易にマルチスレッドプログラミングを行うための方法を解説。

【目次】

- はじめに

- 第 1 章 並列プログラミングを始めるにあたり

- 第 2 章 OpenMP とは

- 第 3 章 OpenMP を使ってみる

- 第 4 章 OpenMP 指示文

- 第 5 章 OpenMP API と環境変数

- 第 6 章 OpneMP の活用例

- 第 7 章 OpenMP スレッドの最適化とデバッグツール

- 第 8 章 他の API やツールとの共存

- 付録 A OpenMP 宣言子一覧

- 付録 B OpenMP API 一覧

- 付録 C OpenMP 環境変数

- 付録 D インテルコンパイラーの OpenMP 関連コンパイラーオプション

- 付録 E OpenMP 2.5 と 3.0 仕様の違い

書籍の宅配をご希望される方は「カットシステム直販案内」をご利用ください。

本書では、インテル Parallel Studio の使い方、特に 2009 年にリリースされたインテル Parallel Composer、インテル Parallel Inspector、インテル Parallel Amplifier の使い方を説明し、それとともに並列プログラミングの基本について解説します。本書は、Microsoft Visual Studio にて C/C++ コンパイラーの利用経験と知識があり、既存のシングルスレッドプログラムのマルチスレッド化を検討されている方々を対象読者としています。

【目次】

- 第1章 並列コンピューティングの概要

- 第2章 インテル Parallel Studio の概要

- 第3章 インストールと設定および起動方法

- 第4章 並列化部分の抽出 ~インテル Parallel Composer の利用(1)

- 第5章 並列化の実装 ~インテル Parallel Composer の利用(2)

- 第6章 並列化部分のデバッグ ~パラレルデバッガー拡張機能の利用

- 第7章 パフォーマンスライブラリー

- 第8章 潜在的バグの探索

- 第9章 プログラムのチューニング

書籍の宅配をご希望される方は「カットシステム直販案内」をご利用ください。

インテル Visual Fortran コンパイラの持つ豊富な機能やさまざまなアプリケーションの作成方法、そして Visual Studio 環境で利用する方法を詳細に解説。 FORTRAN コンパイラの利用経験と知識があり、コマンドラインモードでは使えるが、Visual Studio に統合した利用法がよくわからないというユーザーや、Linux や Mac OS X からWindows への移行を考えているユーザーに最適です。

【目次】

- はじめに、本書の対象読者 (PDF)

- 第 1 章 インテル Visual Fortran 概要 (PDF)

- 第 2 章 インストールとコマンドラインでの利用 (PDF)

- 第 3 章 Visual Studio でのインテルVisual Fortran の利用 (PDF)

- 第 4 章 Visual Studio でのオプションの設定とビルド環境 (PDF)

- 第 5 章 プログラムの実行とデバッグ (PDF)

- 第 6 章 Windows API の利用 (PDF)

- 第 7 章 C/C++ と Fortranの混在 (PDF)

- 第 8 章 Fortran プログラムの最適化 (PDF)

- 第 9 章 他のインテルツールとの共存 (PDF)

- 付録 A コンパイラオプション一覧 (PDF)

- 付録 B 用語集 (PDF)

- 付録 C 関数一覧 (PDF)

- 各章のはじめの数ページを PDF で公開中!

書籍の宅配をご希望される方は「カットシステム直販案内」をご利用ください。