はじめに

このガイドは、次のことを理解していただくことを目的としています。

- インテル® FPGA DPC++ のコードサンプルを、複雑さとユースケースを踏まえて首尾一貫した方法でナビゲートする方法。

- 6 つのエッセンシャル FPGA コードサンプルを使って、FPGA 上で最初の oneAPI アプリケーションを実現する方法。

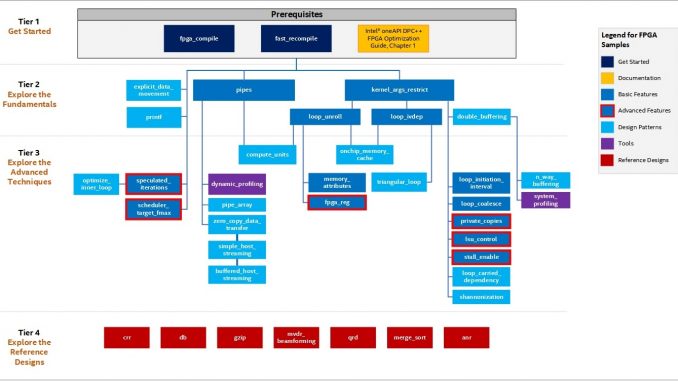

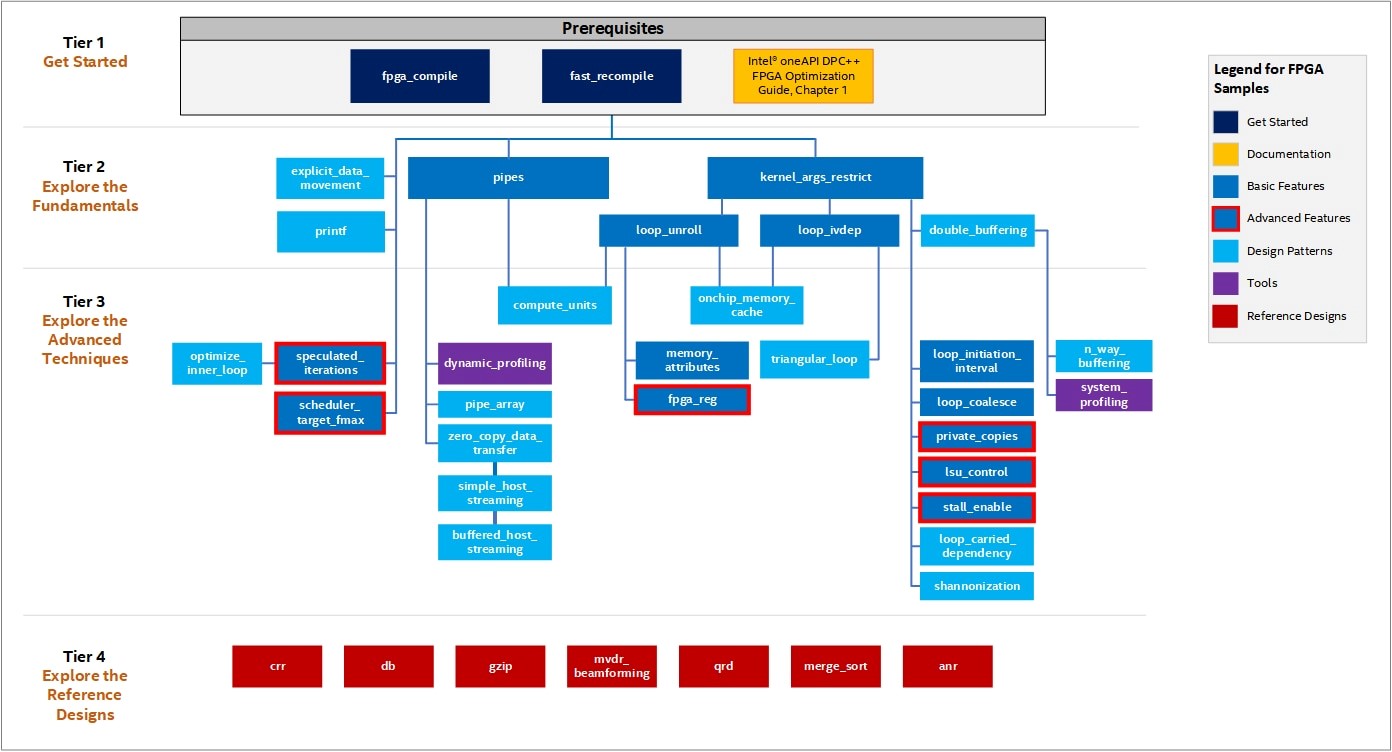

DPC++ FPGA チュートリアル (英語) のフォルダー間の移動には、チュートリアル間の依存関係を示した以下の図を使用してください。

注: 『インテル® oneAPI DPC++ FPGA 最適化ガイド』の「第 1 章: FPGA デザインコンセプト入門 (英語)」は、FPGA の基本的なコンセプトについて説明しており、すべての FPGA 固有のコードサンプルの前提条件となっています。

エッセンシャル FPGA コードサンプル

以下の FPGA サンプルは、FPGA で最初の oneAPI アプリケーションを始めるのに適した有用なチュートリアルのセレクションです。

前提条件

- Khronos* グループによる「SYCL 2020 Provisional Specification」に記載されている SYCL* のコンセプトとアプリケーション・プログラミング・インターフェース (API) についてすでにご存知であること。SYCL* 言語の学習には、オープンアクセスの書籍「 データ並列 C++: C++ と SYCL を使ったヘテロジニアス・システム・プログラミングのための DPC++ をマスターする (英語)」をお勧めします。詳しくは、 SYCL* 仕様書バージョン 2.1 (英語) を参照してください。

- SYCL* アプリケーションを作成した経験があること。詳細については、『インテル® oneAPI プログラミング・ガイド (英語)』を参照してください。

- FPGA で開発する場合に推奨される『インテル® oneAPI DPC++ FPGA 最適化ガイド』の「第 1 章: FPGA デザインコンセプト入門 (英語)」をお読みになっていること。FPGA チュートリアルのほとんどを理解するための前提条件でもあります。FPGA 用データ並列 C++ (DPC++) アプリケーションの性能を最大限に引き出すには、基盤となるハードウェアに精通し、DPC++ アプリケーションを FPGA に変換およびマッピングするコンパイラーの最適化について理解する必要があります。

サンプル・プロジェクトのビルドと実行

FPGA チュートリアルをコンパイルするには、インテル® oneAPI ベース・ツールキットと oneAPI ベース・ツールキット用インテル® FPGA アドオンをダウンロードしてインストールするか、インテル® DevCloud for oneAPI のアカウントを取得する必要があります。

コマンドライン・インターフェイス (CLI) または統合開発環境 (IDE) を使用して、インテル® oneAPI ベース・ツールキットのガイドを開始するには、次のリンクを参照してください。

- コマンドラインを使ってサンプル・プロジェクトをビルドして実行する。

- Linux*

- Windows*

- IDE を使ってサンプル・プロジェクトをビルドして実行する。

- Linux* (Eclipse* もしくは Visual Studio* コード)

- Windows* (Visual Studio*)

- GitHub* (各 FPGA サンプルには、特定の Git リポジトリーへのリンクがあります。詳細は以下のセクションを参照してください。)

サンプル 1:FPGA コンパイルフロー

このサンプルでは、インテル® FPGA デバイスをターゲットとした最も一般的なコンパイルフローを紹介し、各フローを使用するタイミングを説明します。

| CLI または IDE サンプル名 | Git リポジトリーへのリンク |

| fpga_compile | FPGA コンパイルのサンプル (英語) |

サンプルでは、以下のフローを記述しています。

| フロータイプ | アクション |

| 機能的な正しさを検証するためのエミュレーション・フロー | CPU エミュレーター上でプログラムを検証するためにコンパイルする。

|

| 最適化レポートを閲覧するための RTL フロー | FPGA 合成の初期段階で停止し、デザインのパフォーマンス・ボトルネックを短時間で解析する。 |

| FPGA ビットストリームを生成するハードウェア生成フロー | FPGA のハードウェア・ビットストリームを生成し、ホスト (CPU) プログラムに対してリンクする。 |

このサンプルで扱うキーコンセプト:

- DPC++ の FPGA へのコンパイルは、CPU や GPU とどう違うのか、なぜ違うのか

- FPGA デバイスイメージの種類とその使用時期

- FPGA をターゲットにしたコンパイル・オプション

サンプル 2:開発時間の短縮

このサンプルでは、FPGA のコンパイルフローでデバイスリンク機構を使用し、開発時間を短縮する方法を紹介しています。

| CLI または IDE サンプル名 | Git リポジトリーへのリンク |

| fast_recompile | 高速リコンパイルのサンプル (英語) |

インテル® oneAPI DPC++/C++ コンパイラーは、コンパイル時に FPGA デバイスイメージが生成される、FPGA 用の先行コンパイルのみをサポートします。FPGA デバイスイメージの生成処理には数時間かかることがあります。そのため、ホストコードとデバイスコードが一緒にコンパイルされ、ホストコードに変更があった場合、ソースコード全体がこの時間のかかる処理の対象となります。

デバイスリンク機構により、デバイスコードのコンパイルとホストコードのコンパイルを分離することができます。コードの変更がホストのみのファイルにのみ適用される場合、FPGA デバイスイメージは再生成されず、長いコンパイル時間を回避することができます。

このサンプルで扱うキーコンセプト:

- FPGA プロジェクトでホストとデバイスのコードのコンパイルを分けるべき理由

- -reuse-exe フラグの使用方法とデバイスリンクの方法

- プロジェクトに応じてどの方式を選択するか

サンプル 3:カーネル引数のエイリアシングを回避する

このサンプルは、DPC++ [[intel::kernel_args_restrict]] カーネル属性の使用を示しており、カーネル引数がエイリアスでないことを保証できる場合に適用できます (C++ の restrict と類似しています)。

| CLI または IDE サンプル名 | Git リポジトリーへのリンク |

| kernel_args_restrict | カーネルの引数を制限するサンプル (英語) |

ポインター・エイリアシングは、同じメモリー位置に異なる名前 (変数) を使ってアクセスした場合に発生します。ポインター・エイリアシングのため、コンパイラーは、エイリアスの可能性がある操作の並べ替え、並列化、重複化を行う最適化について保守的になります。kernel_args_restrict 属性を使用すると、より積極的なコンパイラー最適化が可能になり、FPGA 上のカーネル・パフォーマンスが向上することがよくあります。

このサンプルで扱うキーコンセプト:

- ポインター・エイリアシングの問題とコンパイラーの最適化におけるその影響

- kernel_args_restrict 属性の動作とカーネルで使用する場合について

- この属性が FPGA 上でのカーネルのパフォーマンスに与える影響

サンプル 4:ループのスループットを向上させることによる最適化

このサンプルでは、DPC++ FPGA プログラムのスループットを向上させるためにループをアンロールする簡単な例を示しています。

| CLI または IDE サンプル名 | Git リポジトリーへのリンク |

| loop_unroll | ループアンロールのサンプル (英語) |

ループアンロールは、ループ内の計算ロジックを複製することでプログラムの並列性を高め、設計のスループットを向上させることができる仕組みです。

このサンプルで扱うキーコンセプト:

- ループアンロールの基本

- プログラム内のループをアンロールする

- プログラムに適したアンロールファクターの決定

サンプル 5:パイプを使ったデータ転送

このサンプルは、パイプという抽象概念を用いてカーネル間でデータを転送する方法を示しています。

| CLI または IDE サンプル名 | Git リポジトリーへのリンク |

| pipes | パイプのサンプル (英語) |

このサンプルで扱うキーコンセプト:

- FPGA 専用 DPC++ パイプ拡張の基礎知識

- DPC++ プログラムでのパイプの宣言と使用方法

サンプル 6:ダブル・バッファリングによる性能向上

本サンプルは、ホスト側の処理とホストとデバイス間のバッファー転送をカーネル実行で並列化し、アプリケーション全体のパフォーマンスを向上させる方法を示しています。

| CLI または IDE サンプル名 | Git リポジトリーへのリンク |

| double_buffering | ダブル・バッファリングのサンプル (英語) |

このサンプルで扱うキーコンセプト:

- ダブル・バッファリング最適化技術

- ダブル・バッファリングが有効な場合の判断

- ダブル・バッファリングの効果を測定する方法

次のステップ

上記のサンプルに目を通した後、依存関係図に基づいて残りの DPC++ FPGA サンプル (チュートリアルまたはリファレンス・デザイン) をご確認いただけます。チュートリアルの多くは、ほかのチュートリアルのコンセプトに基づいて作られていることに注意してください。また、次のリソースも参照してください。

| ドキュメント | 説明 |

| Get Started with Intel® oneAPI Base Toolkit on the DevCloud (英語) | インテル® DevCloud 開発サンドボックス固有の手順については、本ガイドを参照してください。 |

| Installation Guide for Intel® oneAPI Toolkits (英語) | インテル® oneAPI ベース・ツールキットおよび oneAPI ベース・ツールキット用インテル® FPGA アドオンのインストールについて説明します。 |

| Intel® oneAPI Programming Guide (英語) | oneAPI と DPC++ について、プログラミング・モデル、プログラミング・インターフェイス、DPC++ 言語とランタイム、API、ソフトウェア開発プロセスについて学びます。 |

| Intel® oneAPI DPC++ FPGA Optimization Guide (英語) | DPC++ の機能および基礎となるハードウェアを活用し、デザインを FPGA に最適化する方法について説明します。 |

| Get Started with the Intel® oneAPI Base Toolkit for Linux* (英語) | Linux* のスタートアップの手順は、このガイドを参照してください。 |

| Get Started with the Intel® oneAPI Base Toolkit for Windows* (英語) | Windows* のスタートアップの手順は、このガイドを参照してください。 |

| FPGA Tutorials (英語) | チュートリアルの詳しい使い方は、こちらのチュートリアルを参照してください。 |

| DPC++ Foundations Code Sample Walk-Through (英語) | データ並列処理 C++ (DPC++) の基礎に関するコードのウォークスルーは、このガイドを参照してください。 |

| FPGA oneAPI Training (英語) | トレーニング・サイトでは、ウェビナーやクイックビデオをご覧いただけます。 |

| SYCL Specification (v 1.2.1) (英語) | Khronos 社の SYCL* 仕様バージョン 1.2.1 です。 |

| Data Parallel C++: Mastering DPC++ for Programming of Heterogeneous Systems Using C++ and SYCL (英語) | データ並列処理を用いた C++ プログラムの高速化手法を学べるサードパーティー・オープン・アクセスブックです。本書は、コンピューティングを新たなレベルへと押し上げる、このパワフルで重要な新開発の最前線に立つことを可能にします。実用的なアドバイス、詳細な説明、主要なトピックを説明するコード例などが満載です。 |

oneAPI ベース・ツールキット用インテル® FPGA アドオンに関する詳細は以下のボタンからご覧いただけます。

参照記事: Explore DPC++ Through Intel® FPGA Code Samples